- 您现在的位置:买卖IC网 > Sheet目录2000 > IDTCV133PAG (IDT, Integrated Device Technology Inc)IC FLEXPC CLK PROGR P4 56-TSSOP

COMMERCIALTEMPERATURERANGE

IDTCV133

PROGRAMMABLEFLEXPCCLOCKFORP4PROCESSOR

3

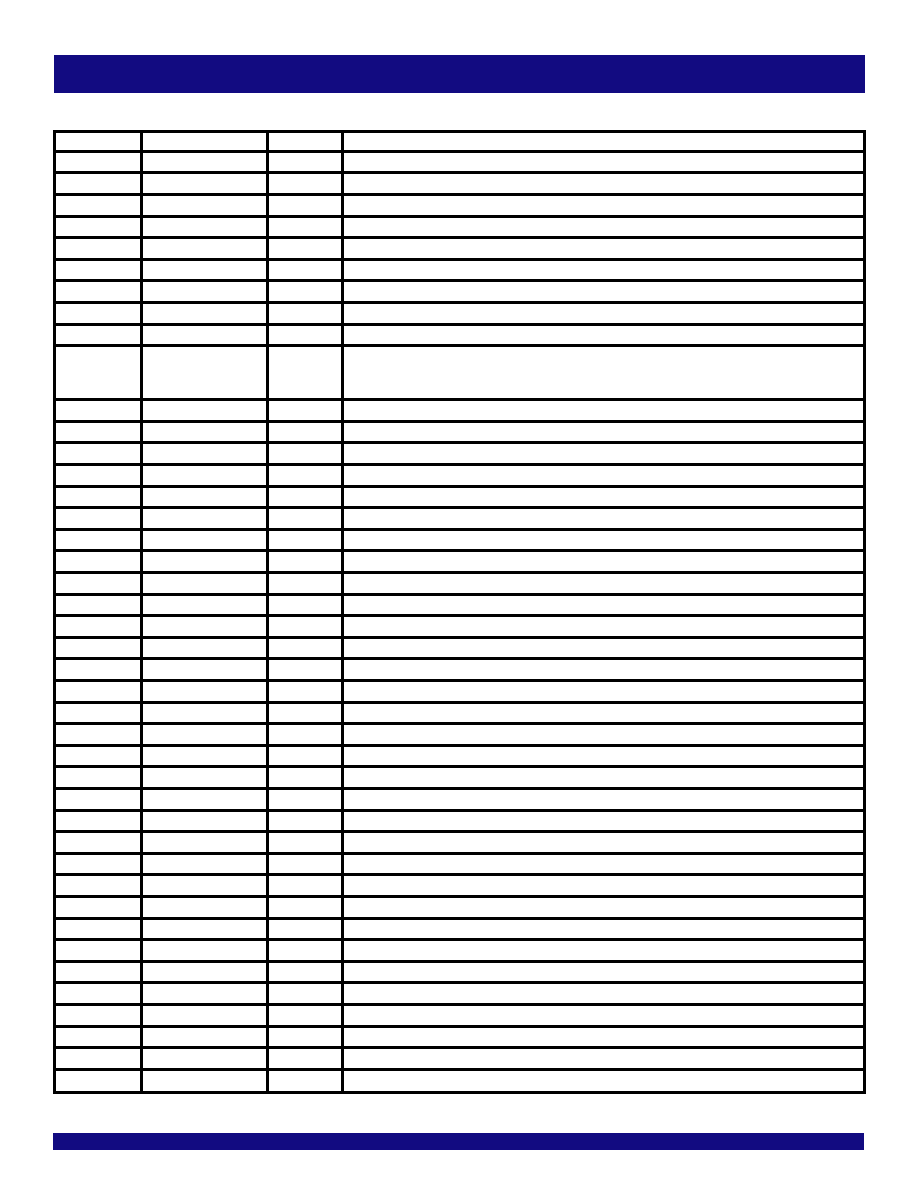

PIN DESCRIPTION

Pin Number

Name

Type

Description

1VDD_PCI

PWR

3.3V

2VSS_PCI

GND

3

PCI1

OUT

PCI clock

4

PCI2

OUT

PCI clock

5

PCI3

OUT

PCI clock

6VSS_PCI

GND

7VDD_PCI

PWR

3.3V

8

PCIF0/ITP_EN

I/O

PCI clock, free running. CPU2 select (sampled on VTT_PWRGD# assertion) HIGH = CPU2.

9

PCIF1/SEL100/96#

I/O

PCI clock, free running. SEL100/96MHz (sampled on VTT_PWRGD# assertion) HIGH, LVDS = 100MHz.

10

VTT_PWRGD#/PD

I N

Level-sensitive strobe used to latch the FSA, FSB, FSC/TEST_SEL, and PCIF0/ITP_EN inputs. After

VTT_PWRGD# assertion,becomesareal-timeinputforassertingpowerdown. (ActiveHIGH). LatchPCIF1/

SEL100/96# input.

11

VDD48

PWR

3.3V

12

USB48/FSA

I/O

48MHz clock/FSA for CPU frequency selection

13

VSS48

GND

14

DOT96

OUT

96MHz 0.7 current mode differential clock output

15

DOT96#

OUT

96MHz 0.7 current mode differential clock output

16

FSB/TEST_MODE

I N

CPU frequency selection. Selects REF/N or Hi-Z when in test mode, Hi-Z = 1, REF/N = 0.

17

LVDS

OUT

Differentialserialreferenceclock

18

LVDS#

OUT

Differentialserialreferenceclock

19

SRC1

OUT

Differentialserialreferenceclock

20

SRC1#

OUT

Differentialserialreferenceclock

21

VDD_SRC

PWR

3.3V

22

SRC2

OUT

Differentialserialreferenceclock

23

SRC2#

OUT

Differentialserialreferenceclock

24

SRC3

OUT

Differentialserialreferenceclock

25

SRC3#

OUT

Differentialserialreferenceclock

26

SRC4

OUT

Differentialserialreferenceclock

27

SRC4#

OUT

Differentialserialreferenceclock

28

VDD_SRC

PWR

3.3V

29

VSS_SRC

GND

30

SRC5#

OUT

Differentialserialreferenceclock

31

SRC5

OUT

Differentialserialreferenceclock

32

CLKREQB#

I N

SRC clock enable (Active LOW, see Byte 21)

33

CLKREQA#

I N

SRC clock enable (Active LOW, see Byte 21)

34

VDD_SRC

PWR

3.3V

35

CPU2_ITP#/SRC7#

OUT

Selectable CPU or SRC differential clock output. ITP_EN = 0 at VTT_PWRGD# assertion = SRC7#.

36

CPU2_ITP/SRC7

OUT

Selectable CPU or SRC differential clock output. ITP_EN = 0 at VTT_PWRGD# assertion = SRC7.

37

VDDA

PWR

3.3V

38

VSSA

GND

39

IREF

OUT

Referencecurrentfordifferentialoutputbuffer

40

CPU1#

OUT

Host 0.7 current mode differential clock output

41

CPU1

OUT

Host 0.7 current mode differential clock output

42

VDD_CPU

PWR

3.3V

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDTCV136PAG

IC FLEXPC CLK ATI RS400 56-TSSOP

IDTCV137PAG

IC FLEXPC CLK AMD K8 56-TSSOP

IDTCV142PAG

IC FLEXPC CLK PROGR P4 56-TSSOP

IDTCV146PVG

IC FLEXPC CLK PROGR P4 56-SSOP

IDTCV149PAG

IC FLEXPC CLK PROGR K8 56-TSSOP

IDTNW6005ASG

IC CALLER ID DECODER 20SOIC

IDTNW6006AS

IC CALLER ID DECODER 20-SOIC

IDTSSTE32882HLBBKG

IC REGISTERING CLK DRIVER 176BGA

相关代理商/技术参数

IDTCV133PAG8

功能描述:IC FLEXPC CLK PROGR P4 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

IDTCV136PAG

功能描述:IC FLEXPC CLK ATI RS400 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV136PAG8

功能描述:IC FLEXPC CLK ATI RS400 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™, PCI Express® (PCIe) 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

IDTCV137PAG

功能描述:IC FLEXPC CLK AMD K8 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV137PAG8

功能描述:IC FLEXPC CLK AMD K8 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™, PCI Express® (PCIe) 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

IDTCV140

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:PROGRAMMABLE FLEXPC CLOCK FOR P4 PROCESSOR

IDTCV141PAG

功能描述:IC CLK BUFFER 1-8 DIFF 48-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6

IDTCV141PAG8

功能描述:IC CLK BUFFER 1-8 DIFF 48-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件